Real-time Application Solution for RISC-V Core on Forlinx Embedded T113-i Development Board

As market demands for embedded devices continue to rise, there is an increasing number of master control solutions that integrate embedded processors and real-time processors to better balance performance and efficiency. In these solutions, the real-time core handles high-real-time tasks, while the A-core processes complex tasks, and real-time data exchange between the two cores is required. However, in data transmission, traditional serial interfaces, although cost-effective, have relatively slow transmission speeds. On the other hand, parallel interfaces offer faster speeds but come at a higher cost. Therefore, multi-core heterogeneous processors on a single chip have become an ideal choice to meet these demands.

RISC-V, as an open-source instruction set architecture, provides strong support for real-time processing scenarios due to its simplicity, consistency, scalability, and high compilation efficiency. Combining the A-core with the RISC-V core as a single-chip multi-core heterogeneous solution effectively leverages the advantages of RISC-V, achieving a harmonious combination of high performance and high real-time performance.

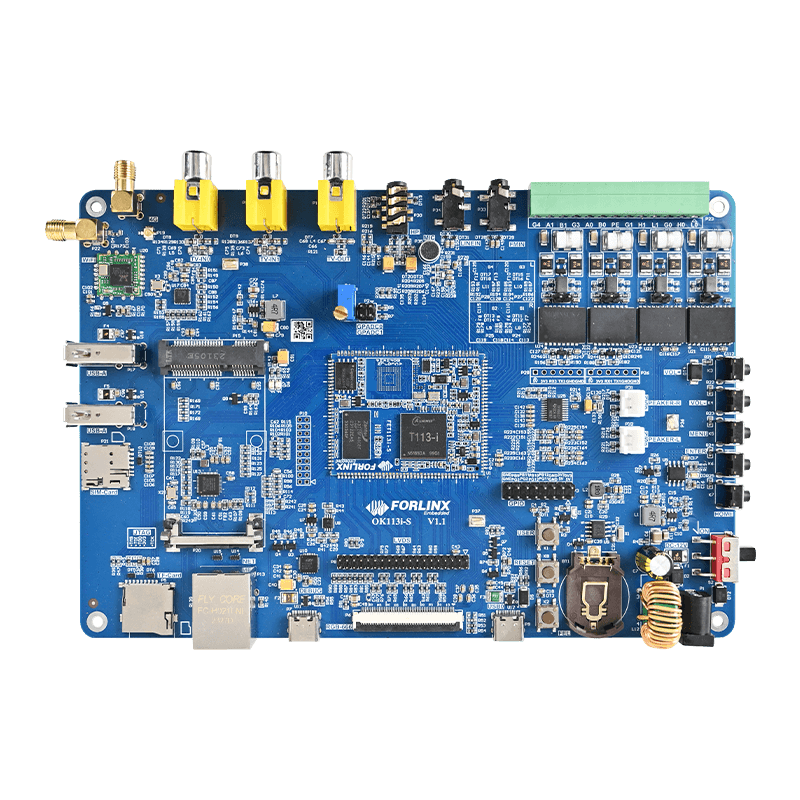

This article takes the OK113i-S development board as an example to introduce the resources and application cases of the RISC-V core.

1. RISC-V Core on OK113i-S Development Board

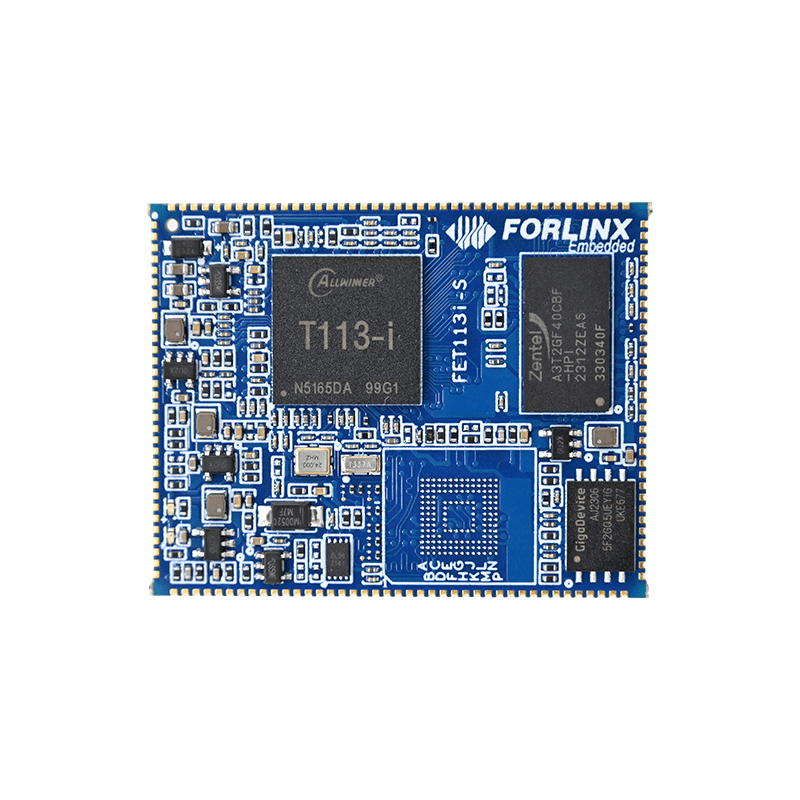

Forlinx Embedded OK113i-S development board is a cost-effective development board based on the Allwinner T113-i industrial-grade processor. It integrates a dual-core Cortex-A7 CPU, a 64-bit XuanTie C906 RISC-V core, and a DSP, providing efficient computing capabilities and high cost-effectiveness. Particularly noteworthy is its built-in RISC-V core, which, as an ultra-high-efficiency real-time processor, can reach a peak frequency of 1008MHz. It is equipped with a standard memory management unit, enabling smooth operation of RTOS systems or bare-metal programs, further enhancing application flexibility.

1.1 Characteristics of the RISC-V Core

- (1) Maximum frequency of up to 1008MHz;

- (2) 32KB instruction cache;

- (3) 32KB data cache;

- (4) Capable of running in large-capacity DDR…

1.2 Interface Resources of the RISC-V Core

|

Function |

Description |

|---|---|

|

GPIO output |

GPIO output (e.g., controlling relays, etc.) |

|

GPIO Input Interrupt |

Captures important signals |

|

I2C |

Supports data transmission as a host; can connect to various slaves (e.g., RTC chips, EEPROMs, etc.) |

|

SPI |

Supports SPI master mode; supports both interrupt and DMA modes |

|

UART |

Supports SPI master mode; supports both interrupt and DMA modes |

|

Inter-core Communication |

Supports communication between the A-core and RISC-V core; small data transmission via RPMsg and large data transmission via RPBuf |

|

DDR Operation |

Supports RISC-V programs running on large-capacity DDR (available space: 35M+) |

|

HTIMER |

Supports general-purpose timers (us level) and high-precision timers (ns level) |

|

PWM |

Supports PWM output with different periods and duty cycles |

|

GPADC |

Supports general-purpose 12-bit ADC sampling |

|

OS |

Supports general-purpose 12-bit ADC sampling |

2. Application Examples

2.1 SPI Data Sending and Receiving

This case involves an SPI loopback test, where the MOSI and MISO pins of the SPI are shorted to perform data transmission and reception.

(1) Function Introduction

(2) Achievement of Results

Both the SPI transmission and reception FIFOs have a capacity of 64 bytes. In the underlying HAL library program, an interrupt method is used when the data length is less than 64 bytes, while a DMA mode is employed when the FIFO is greater than or equal to 64 bytes.

Interrupt Method Transmission Effect:

DMA Method Transmission Effect:

In the DMA transmission mode, the SPI speed defaults to 5M bit/s. In this example, the average transmission speed is 580.43KB/s, equivalent to 4.6M bit/s, close to the theoretical value.

2.2 Inter-core Communication RPBuf

RPBuf is a high-bandwidth data transmission framework implemented by Allwinner based on RPMsg. RPMsg is an inter-core communication mechanism based on shared memory and Msgbox interrupts. Excluding the 16-byte header, RPMsg can transmit up to 496 bytes of valid data per transmission. Therefore, Allwinner has implemented a large-scale data transmission mechanism, RPBuf, based on RPMsg. The principle is to place the transmission data in DDR, then transmit the DDR address and size through RPMsg. We demonstrate a single transmission of 32KB of data as an example.

(1) Function Introduction

- VirtIO: A virtualization data transmission framework for managing shared memory VRING;

- VRING: A circular shared memory managed by VirtIO;

- Msgbox: A message interrupt mechanism provided by Allwinner, which is compatible with the native mailbox framework in the Linux kernel;

- MSGBOX_IRQ:Msgbox interrupt;

- RPMsg: A small data transmission framework based on VirtIO-managed shared memory;

- RPbuf: A large data transmission framework implemented by Allwinner based on RPMsg.

From the diagram (taking data transmission from the RISC-V core to the A-core as an example), RPbuf first places the data in DDR, then sends the buffer’s starting address and size to the A-core via RPMsg (RPMsg places the buffer’s starting address and size into VRING and then requests a Msgbox interrupt. Upon receiving this interrupt, the A-core retrieves the cmd using the RPMsg interface function in the callback).

A-core then obtains the address and length within the buffer from the cmd handler and finally reads the data at the application layer, completing the data transmission between the two cores.

(2) Application Demonstration

From the test results shown above, the bandwidth is approximately 27~30Mbps.

These are the methods for using the peripherals of the RISC-V core on the Forlinx Embedded OK113i-S development board. Does it feel as simple and convenient as developing with a microcontroller?

Dear friends, we have created an exclusive embedded technical exchange group on Facebook, where our experts share the latest technological trends and practical skills. Join us and grow together!