FET113i-S SoM Now Supports RISC-V, Offering a Superior Cost-Effective Solution

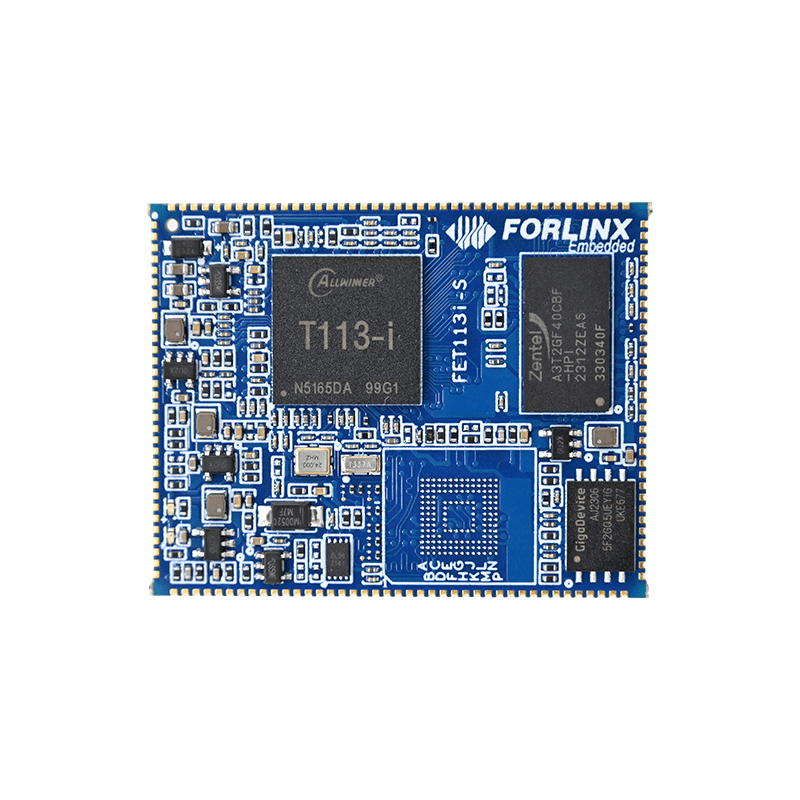

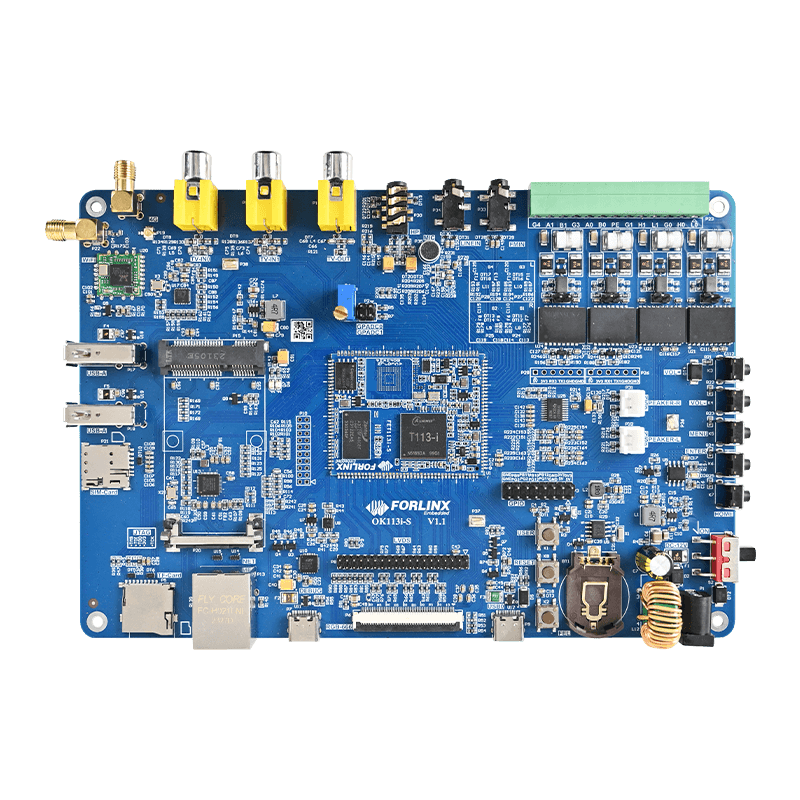

FET113i-S is an industrial-grade SoM designed by Forlinx Embedded based on Allwinner T113-i processor. With excellent stability and ultra-high cost performance, FET113i-S SoM has gained wide attention from customers. As a multi-core heterogeneous architecture chip with an A7 core, a RISC-V core, and a DSP core, Allwinner Technology recently released the RISC-V core (XuanTie C906) details for the T113-i, and Forlinx embedded quickly adapted to this development.

1. What is RISC-V?

RISC-V is an open-source instruction set architecture (ISA) based on the principles of Reduced Instruction Set Computing (RISC). It was first introduced by the University of California, Berkeley in 2010 and has since gained significant attention and support from academia and industry worldwide. RISC-V architecture, characterized by its openness, simplicity, and scalability, is emerging as a formidable force in the global semiconductor industry.

2. What Are the Advantages of the T113-i's Risc-v?

High Efficiency and Low Power Consumption

RISC-V architecture follows the principles of reduced instruction set computer, which simplifies the hardware design, improves the execution efficiency and reduces the development cost. The RISC-V cores in the T113-i processor can efficiently perform a wide range of computational tasks while maintaining low power consumption, making it ideal for resource-constrained edge computing environments.

Modularity and Scalability

RISC-V architecture is designed with simplicity and modularity in mind, allowing different instruction set extensions to be chosen based on requirements. RISC-V core in the T113-i processor supports multiple standardized extension instruction sets, such as M (integer multiplication and division), A (atomic operations), and F/D/Q (single/double/quad-precision floating-point operations), enabling flexible combination and addition according to specific application scenarios.

Open Standard and No Licensing Fees

RISC-V is open source, allowing anyone to use and extend it for free, without licensing fees. This greatly promotes technology sharing and innovation, reducing product development costs.

Real-Time Performance

In the T113-i, the A7 core, RISC-V core, and DSP core can run simultaneously, realizing multi-core heterogeneous computing. This design enhances overall system performance and meets diverse application requirements. The RISC-V core, in particular, can accommodate applications with high real-time requirements, ensuring rapid response and processing of real-time data.

3. A Quality Choice for Cost Reduction

Forlinx Embedded FET113i-S SoM, with completed RISC-V core adaptation, is highly competitive in price. Its industrial-grade quality enables it to handle more complex application scenarios, while its comprehensive peripheral interface resources make it both powerful and user-friendly.

FET113i-S SoM's clear advantages, combined with Folinx Embedded's stable supply chain and robust technical support, ensure swift project implementation and market primacy for customers.