i.MX6UL Development Board Pin Multiplexing Parameter Configuration Method (PINMUX)

The peripheral resources of NXP Cortex-A7 i.MX6UltraLite are very rich. However, I need to remind everyone that these interfaces cannot be used at the same time. In order to provide the cost-effectiveness of the chip, the CPU manufacturer introduced the PINMUX architecture. Simply put, the pins are multiplexed. The above-mentioned interfaces only used about 114 Each pin can have 9 functions at most, and each function can appear on different pins.

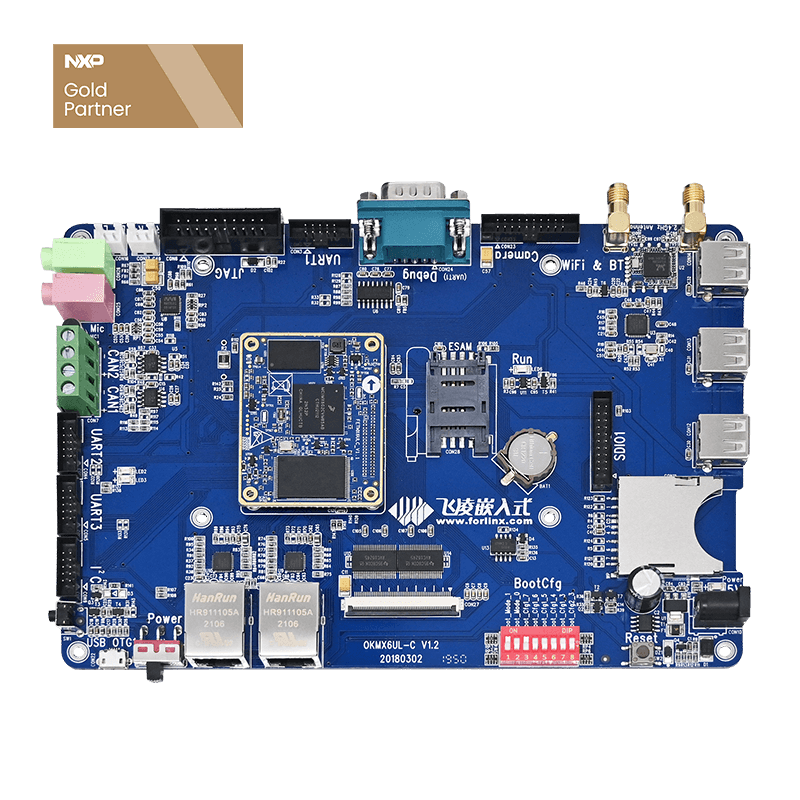

The hardware platform used in this development is the Forlinx Embedded OKMX6UL-C development board. Please refer to other boards as appropriate. The specific implementation steps are as follows:

arch/arm/boot/dts/imx6ul-pinfunc.h

arch/arm/boot/dts/imx6ul-14x14-evk.dts

Expand the pin configuration to: 0x0158 0x03E4 0x0000 1 0 0x1b0b1

0x0158 | 0x03E4 | 0x0000 | 0x1 | 0x0|0x1b0b1

---------------------------------------------------------------------------------------------------

mux_ctrl_ofs | pad_ctrl_ofs | sel_input_ofs | mux_mode | sel_input| pad_ctrl

How are the above parameters determined in the reference manual?

The following takes LCD_DATA16 multiplexed as UART7_DCE_TX as an example to illustrate the method of multiplexing pin parameter configuration

For the configuration of multiplexed pins, you should find it in the manual pin multiplexing section (IOMUXC). But it is convenient to determine the pad name, so it is defined in the chapter of External Signals and Pin Multiplexing. Searching for the middle part "LCD_DATA16" of MX6UL_PAD_LCD_DATA16__UART7_DCE_TX can jump directly to the register chapter of the LCD_DATA16 pin.

pad_ctrl_ofs is 0x03E4, and according to this configuration pad_ctrl is 0x1b0b1 (configure pull-up resistance, frequency, etc.):

input_ofs finds the part ending with SELECT_INPUT in the IOMUXC chapter, and selects UART7_DCE_RTS in the middle. If there is no sel_input_ofs=0x000, then the corresponding sel_input is 0.

If there is, for example, MX6UL_PAD_ENET1_RX_ER__UART7_DCE_RTS, as shown in the figure below, so the sel_input_ofs of ENET1_RX_ER=0x650. So ENET1_RX_ER (MX6UL_PAD_ENET1_RX_ER__UART7_DCE_RTS) sel_input=0x1.

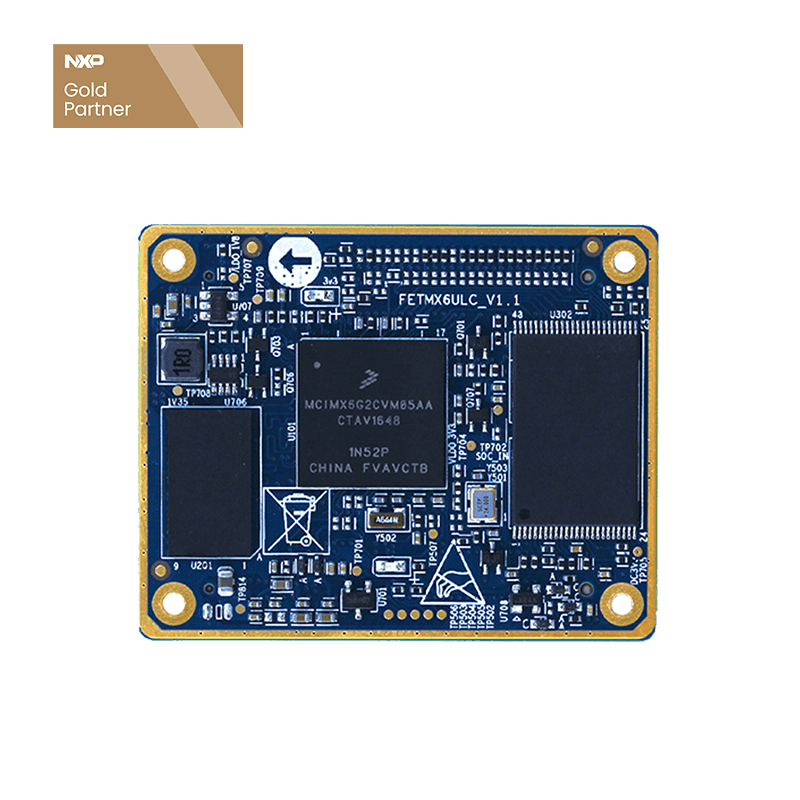

For more i.MX6UL information, please pay attention to FETMX6UL-C core board details